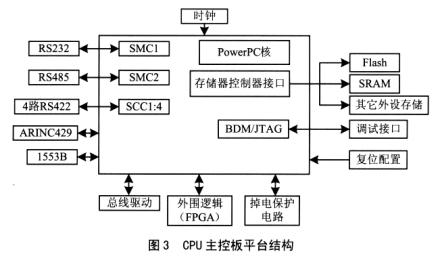

2.1 主控机系统

主控机系统采用的系统时钟为50MHz的MPC860P。它的总线接口的工作电压是 3.3V,兼容5V TTL电平。

MPC860 PowerQLJlCC微处理器是一个多用途的通用芯片,内部集成了微处理器和常用外围组件,可用于各种控制领域,特别适用于通信产品。MPC860集成 了嵌入式PowerPC核和一个为通信使用的专门的RISC的通信处理器模块(CPM)。MPC860的CPM支持6个串行通道(4个串行通信控制器 SCC、2个串行管理控制器SMC、1个I2C(Inter-Integrated Circuit)接口和1个串行外围接口电路(SPI)。MPC860还提供1个快速以太网控制器,可以支持10Mbps到100Mbps的以太网。由于 CPM分担了嵌入式PowerPC核的外围工作任务,这种双处理器体系结构比传统体系结构的处理器具有更高的效率和更高的可靠性。图3为主控系统结构。

图3中,MPC860P内部的串行管理控制器SMCl和SMC2分别用来作为R$232和RS485的UART接口,4个串行通信控制器(SCc1、 SCC2、SCC3、SCC4)用于控制Rs-422接口。所有的存储器及外部存储设备均通过存储器控制器与MPC860P接口。

MlPC860P通过内存控制器GPCM与SRAM建立接口。这里选用的是三星公司的K6X8008C2B,用4片×8位组成32位SRAM 数据总线供系统使用。 对于Flash闪存配置的设计方案,将其分成两块:一块用来装载引导系统启动的PPcB00T及裁减后的CRTOS 2.0操作系统;一块用来放置上层应用程序,作为用户数据区域,保存每次飞机起飞降落中的燃油数据。Flash选择Intel公司的28F640J3A, BGA封装。这块芯片有23根地址线,16根数据线,容量为8MB,128KB的可擦除块;擦除块之间相互独立,每一块的擦除操作可在1s内完成,并可单 独被擦写100 000次;支持8位及16位两种数据宽度工作模式,通过其上的丽位的高低电平来选择。在采用8位数据宽度模式时,BRTE位置低位,有效地址线为 A0~A22;采用16位数据宽度模式时,BYTE位置高位,此时A0位悬空无效,有效地址线为A1~A22。在此我们采用16位数据宽度模式。

由此看到MPC860的强大通信功能。我们将SCC1到SCC4四个通信口作为4个RS422通信口,选用TI公司的AM26LS32(接收器)和 AM26LS31(发送器)。其均遵从ANSIEIA/TLA-422-B规范,采用十5V工作电源,兼容TTL电平,16引脚DIP封装。 AM26LS32在通用模式下输入电平范围可达7V,灵敏度可达200mV,三态输出。用仲裁电路的仲裁控制输出TS1GATE和TSIGATE来控制 AM26LS32和AM26LS31的工作使能端,以达到控制双机竞争通信信道的目的。

将SMCl配置成一个RS232C口,器件选用引脚完全及功能完全与之兼容的MAx232芯片。

将SMC2 配置成一个RS485,以便与其它航空设备通信。器件选用MAx485,8引脚SO封装。由于采用二线制方式,半双工通道,设计上用经过16244驱动的 CPU读写信号BRD/WR来连接MAX485的面和DE端,以此达到控制MAx485的发送和接收状态。

为了使系统具有更强的兼容能力,还提供了目前两个航空通信标准接口一ARNIC429和1553B。

为实现1路ARINC429通信接口,选用Intersil公司的HS-3282及HS-3181芯片。HS-3282是429总线通道控制器,主要控制 429接口与CPU端的接收与发送,40引脚DIP封装。因为外围控制逻辑及片选比较复杂,因此设计在FPGA内部来实现。HA-3281是429总线的 电平控制驱动器,其实现429与通信信道的电平转换与物理连接。429通道的接收分别占用CPU的IRQ5和Q6中断源。

为实现1路 1553B总线接口,选用DDC公司的BU-61580总线控制芯片,+5V工作电压,完全集成MIL-STD-1553接口及终端,灵活的处理器及内存 配置接口,内配标准4K×16RAM。由于在设计中给其分配的地址空间范围内有多个外设,所以在FPGA用CS7加上一定的地址经译码后产生 的信号BU SEIECT作为Bu-61580的片选信号。由于此芯片工作需要独立的16MHz时钟信号源,因此采用一个有源的16MHz石英振荡器。

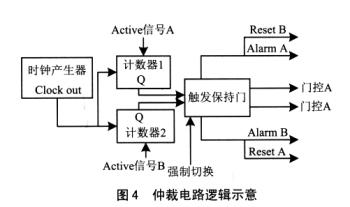

2.2 仲裁电路

仲裁电路是为保证双机热备系统的正常工作及出错板极切换而设计的,所以尤为重要。

(1)设计思路

用两个可编程计数器不断对时钟脉冲进行计数,当到达预定计数值而未收到CPU端ACtive信号时,则在计数输出端产生从低电平到高电平的跃变。该变化通过门电路决定是否触发用于切换输出信号的触发器,同时给出故障警示脉冲信号。

(2)电路逻辑说明

如图4所示,晶振和两个非门组成的自激多谐振荡器产生的时钟脉冲(32.768kHz),分别送到两个可编程计数/分频器54LS292的时钟输入端。 因此定时周期为2s,则计数器Q端在半个周期即1s时翻转。如超过该时间而CLRN未收到从CPU板送来的Active信号(下降沿有效),则会在Q输出 上升沿。两个Q端输出分别送到两个与非门用于判断是否输出触发J-K触发器的下降沿信号。当有超时信号输出的这一边正好是其输出有效的一边时,其送往的与 非门的另一输入必为高。这时触发信号产生,触发器被触发而产生切换。反之,当有超时信号输出的这一边不是其输出有效的一边,则其送往的与非门的另一输入必 为低,这时不产生触发信号,不发生切换。在两种情况下产生的超时信号都被送往两个与非门组成的组合逻辑电路,用于输出故障警示脉冲到当前正常工作的CPU 板的A1arm端,同时这个信号也作为发生故障的CPU板的复位信号送往对应的CPU复位端。

2.3 其它硬件部分的设计

本系统的硬件设计部分还包括A/D和D/A转换、频率计数输入端口、开关量转换电路、掉电保护电路、测试诊断电路等。由于测试诊断电路涉及的内容较多,故在此未赘述,仅对前四部分作简要介绍。

为实现A、B通道的64路A/D采集模拟开关控制电路(其中四路用作器件工作状态测试),选用ADl674作为A/D转换器件。AD1674是美国模拟器 件公司(Analog Devices)生产的12位精度逐次逼近型快速A/D转换器,为其公司经典转换器AD574A的升级产品。转换速度仅为10 u s,转换精度≤005%,片内配有三态输出缓冲电路,因而可直接与各种典型的微处理器相连接,而无须附加逻辑接口电路,且能与CM0S及TTL电平 兼容。另外其片内自带采样保持电路,保证了A/D采样的准确性和稳定性,可直接与被转换的模拟信号相连。由于ADl674片内包含高精度的参考电压源和时 钟电路,这使它在不需要任何外部电路和时钟信号的情况下能完成一切A/D转换功能。

本系统中的4路频率端口信号量(FQ0~FQ3) 经4路差分比较器整形成4路标准TTL方波信号(FQINO~FQIN3,门限以TTL电平为准),后送入CPU计数器计数。差分比较器选用TI公司的 LMl39芯片。其支持单极和双极输入,宽电源输入(+2V~+36V),差分输入电压范围可达36V,输出电平兼容TTL、MOS、CMOS,内部集成 4通道比较器,采用14引脚DIP封装。

根据系统工作环境,32路离散量的输入采集信号及输出控制信号均为+28V;而MPC860的工作电压为3.3V输入电平兼容+5V,涉及到高低电平的隔 离控制,因此设计中采用光耦器件来实现。我们选用Toshiba公司的TLP521-4,片内集成4路耦合通道,整个系统输入输出共需16片,集电极至发 射极最高电压+55V,片内二极管正向电流最大50mA,功耗150mW,16引脚DIP封装。

根据方案要求,系统在掉电时需要提供短时间的电 源以作系统数据保存工作。这里选用Maxim公司的 MAx79l电路监控芯片,采用IRQ1中断源,配合大容量 的电解电容作为后备电源。

2.4系统自诊断辅助电路

为了配合系统自诊断程序的工作,设计了以下四个 方面的辅助电路测试电路。

(1)模拟量输入测试模块

通过提供一个检测用模拟信号,作为多路模拟开关的一路输入信号。经A/D转换后,将数据送入CPU进行比较检测,便可得知模拟信号输入模块是否正常工作。

(2)A/D本身的故障定位

各种典型的A/D转换器,都有两个重要的信号引脚START和EOC(以常用的AD0809为例),前者为输入信号,高电平有效。此信号上升沿清除ADC 内部寄存器,在下降沿时启动内部控制信号,开始A/D转换工作。另一信号EOC是转换结束信号,高电平有效,为输出信号。当一次A/D结束时,此引脚输出 高电平。在A/D转换过程中为低。我们可以利用它来测试A/D是不是正常工作。具体到我们系统所选用的芯片AD574而言,它的EOC信号引脚称为 STS。不同的是,A/D转换过程中为高电平,转换结束为低电平。

(3)频率输入测试模块

本模块主要由频率输入调整及MPU构成。MPC860发出基准频率后输入调整模块后再送入MPC860内部频率计数器进行计数及比较。

开关量输入测试模块。本模块通过MPU主动发出一个数据信号,经由开关量输入模块通道后再返回CPU内部进行比较。如果与原来发出的开关量相符,为正常工作状态。

(4)通信端口测试模块

主要思想是通过引入一个类似于双刀双掷的电子开关,然后让系统发信息给自己。能正常接收为正常工作,反之表明系统有错。

3 总 结

本文所设计的机载燃油双机热备份测控计算机系统,已实现预期容错功能,具有通用性强,系统可靠性高、功耗低等诸多特性。目前,该系统在嵌入式安全实时操作系统CRT0S2.0的支持下,正在开发燃油测控和管理等更多的上层应用软件。

|

![]()